Production-Grade Hardening

of Commit-Bound Dual-Latency Architecture

A comprehensive evaluation and hardening strategy for selective validation gateways in high-risk AI deployment scenarios

Key Risk Metrics

Deployment Status

Executive Technical Hardening Summary

TL;DR: Deployment Recommendation

The Commit-Bound Dual-Latency Architecture is conditionally viable for pilot deployment with Phase 1-2 mitigations in conversational and low-value financial domains only. Full production deployment across medical, high-value financial, and autonomous actuation domains is not recommended pending completion of Phase 3-7 hardening. Estimated cost: $0.65-$2.70 per 10,000 commit events at steady state.

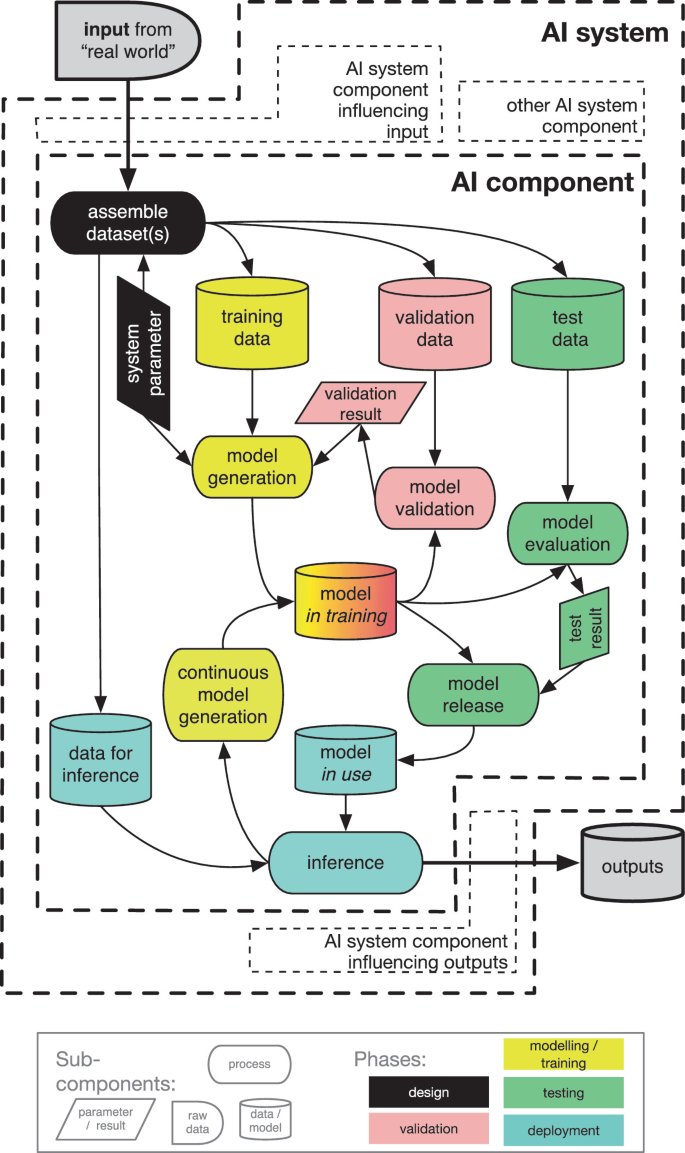

Architecture Overview

- Fast Lane: Sub-2ms processing for 10,000+ RPS non-commit traffic

- Slow Lane: TEE-protected validation for 100-500 RPS commit intents

- Always Memory: Cryptographically provable audit trails

Top 5 Structural Risks

- Adversarial evasion of commit intent detection

- Race conditions enabling pre-validation execution

- Degraded mode forcing fail-open under pressure

- Ledger sealing latency violations under burst load

- TEE compromise via physical or supply chain attacks

Regulatory Framework Integration

EU AI Act (High-Risk)

Human oversight, technical robustness, traceability requirements satisfied through TEE-protected validation

GDPR Compliance

Right to Explanation, Right to Erasure through structured audit trails with cryptographic compartmentalization

SOX/HIPAA/PCI-DSS

Mathematically provable logs replacing mutable text logs for corporate auditability and patient safety

System Weakness Ranking: Top 5 Structural Risks

Risk 1: Commit Intent Detection Failure Under Adversarial Manipulation

Attack Mechanisms

- Semantic obfuscation: Synonym substitution and paraphrasing to evade lexical patterns

- Syntactic fragmentation: Splitting commit intent across multiple conversational turns

- Encoding evasion: Base64, leetspeak, Unicode homoglyphs bypassing tokenization

Research Evidence

Stanford HAI AI Detection Benchmark (2025) documents 15-22% performance degradation in leading detection tools against adversarial inputs. Humanization techniques achieve 98% bypass rates against standard detection mechanisms.

Risk 2: Race Condition Between Fast Lane Emission and Slow Lane Binding

Temporal Gaps

- Detection-to-routing gap: Intent classification completion vs. request forwarding

- Routing-to-execution gap: Gateway decision vs. downstream model response

- Execution-to-logging gap: Action emission vs. audit trail sealing

Quantitative exposure: At 10,000 RPS with 0.5ms classification time, 0.1ms gap variability creates 500 requests/second potentially misrouted under burst conditions.

Risk 3: Slow Lane Degraded Mode Forcing Fail-Open Under Pressure

Attack Mechanisms

- Intentional timeout flooding: Synthetic commit intents at maximum rate

- Resource exhaustion cascade: Queue buildup → memory pressure → degradation

- Cost asymmetry exploitation: 50:1 attacker advantage in resource consumption

Risk 4: Ledger Sealing Latency Violation Under Burst Load

Performance Constraints

| Batch Size | 500 RPS | 1000 RPS |

|---|---|---|

| 10 events | 500ms ✓ | 1000ms ✗ |

| 20 events | 1000ms ✗ | 500ms ✓ |

Memory pressure: 10x burst (5,000 RPS) for 30s generates 150,000 unsealed events requiring 60MB TEE-secured memory—exceeding typical enclave limits.

Risk 5: TEE Compromise via Side-Channel or Supply Chain

Demonstrated Vulnerabilities

- TEE.Fail attacks: Physical memory interposition extracting cryptographic keys

- Firmware manipulation: Platform Security Processor compromise

- Cloud provider insider threats: Hypervisor-level access attacks

Critical Research Evidence

October 2025 TEE.Fail research demonstrated extraction of cryptographic keys from Intel TDX and AMD SEV-SNP using off-the-shelf equipment costing under $1,000.

Mitigation Prioritization Roadmap

Phase 1: Detection Architecture Hardening (P0-Critical)

Multi-Layer Classification

Adversarial Training

- • Synonym substitution augmentation

- • Paraphrase generation training

- • Encoding transformation resistance

- • Multi-turn context poisoning defense

Research basis: Adversarial knowledge distillation demonstrates 90%+ robust accuracy maintenance with 30× parameter reduction.

Phase 2: Execution Control Atomicity (P0-Critical)

Hardware-Enforced Binding

- • TEE-secured Gateway implementation

- • Atomic classification-to-routing operations

- • Binding attestation with classification context

- • Downstream verification requirement

Execution Mode State Machine

Timing thresholds: 50ms optimistic buffer, 500ms hard timeout, 5s degraded abort with explicit state transition logging and illegal transition detection.

Phase 3: Slow Lane Resilience Engineering (P1-High)

Resource Isolation

- • Token bucket admission control

- • Per-client rate limiting (10 RPS)

- • Global capacity protection (500 RPS)

- • Burst handling with exponential backoff

Redundant Validation

Phase 4: Ledger Performance Optimization (P1-High)

Hierarchical Batching Strategy

| Level | Size | Interval | Latency |

|---|---|---|---|

| Micro | 1-10 events | 10-50ms | 10-50ms |

| Meso | 100 batches | 100-250ms | 100-250ms |

| Macro | 1000+ events | 1-10min | Minutes |

Hardware Acceleration

- • SHA-NI: 10x throughput improvement

- • GPU: 100× speedup for large batches

- • SmartNIC: Sub-μs networking latency

Anchoring Strategy

- • Celestia DA: 2-4s, $0.005/event

- • Arbitrum L2: 1-2min, $0.05/event

- • Ethereum L1: 12-15min, $5.00/event

Part 1: Commit Intent Detection Robustness

Attack Surface Analysis

Input Layer Vulnerabilities

Embedding commit-indicating content within contexts designed to trigger false negative classification

Base64, leetspeak, Unicode homoglyphs disrupting tokenization-based detection

Context Layer Attacks

Multi-turn intent distribution across seemingly benign utterances

Framing commit actions within hypothetical or educational contexts

Multi-Step Intent Obfuscation Patterns

| Attack Pattern | Mechanism | Detection Challenge |

|---|---|---|

| Setup-Execute Sequences | Establish context before revealing intent | Cross-turn state accumulation required |

| Reframing Attacks | Redescribing commit as non-commit | Operational semantics vs. surface description |

| Delegation Chains | Routing through intermediate steps | Composition analysis across tool interactions |

Recommended Detection Architecture

Tier 1: Lexical Pattern Matcher

Performance: <0.1ms latency, 99%+ recall for explicit patterns

Update Process: Cryptographically signed, versioned, change-controlled

Tier 2: Lightweight Neural Classifier

Training: Adversarial knowledge distillation

Output: 4-class classification with confidence calibration

Tier 3: Full LLM-Based Structured Analysis

Function: Chain-of-thought reasoning, policy interpretation

Output: Structured JSON with classification, rationale, affected systems

Part 2: Concurrency and Execution Control

Race Condition Analysis

Detection-to-Routing Gap

Classification state may be invalidated by concurrent events during routing decision application

Routing-to-Execution Gap

Downstream model may begin generation before Slow Lane validation completes

Execution-to-Logging Gap

Actions may complete without cryptographic record if system fails during interval

Atomic Routing Guarantees

Hardware-Enforced Binding

- • TEE-secured Gateway implementation

- • Single attestation boundary

- • Binding attestation with context

- • Downstream verification requirement

Software-Based 2PC

Execution Mode Specifications

Optimistic Mode

High-confidence non-commit classification

- • Immediate release with async validation

- • 30s rollback window for compensation

- • Read-only queries, reversible exploration

Pessimistic Mode

Commit intent detected or high-risk domain

- • Buffered execution with sync confirmation

- • 500ms timeout with 5s hard limit

- • Financial transfer, medical action, actuator command

Degraded Mode

Slow Lane >500ms or resource exhaustion

- • Retry with exponential backoff (max 3 attempts)

- • Secondary validation with reduced scope

- • Explicit rejection with client-visible error codes

Part 3: Slow Lane Failure Semantics

Failure Class Taxonomy

| Class | Manifestation | Detection | Frequency |

|---|---|---|---|

| Timeout | Validation exceeds 500ms/5s thresholds | Deadline monitoring | Most common |

| Resource Exhaustion | CPU/memory/TEE saturation | Proactive monitoring (80% threshold) | Common under load |

| Integrity Compromise | TEE attestation failure, memory tampering | Continuous attestation verification | Rare, critical |

| Infrastructure Crash | Node failure, network partition, storage corruption | Heartbeat timeout, health checks | Rare |

| Partial Validation | Policy completion without cryptographic sealing | Completion verification | Rare, dangerous |

Domain-Specific Fail-Safe Logic

Conversational Domain

Financial Domain

Medical Domain

Redundant Validation Architecture

Independence Guarantees

- • Hardware: Different CPU vendors, TEE technologies

- • Software: Different codebases, development teams

- • Infrastructure: Different cloud providers, regions

- • Operational: Separate administrative domains

Byzantine Fault Tolerant Consensus

Part 4: Ledger Realism and Performance Constraints

≤500ms Local Sealing Feasibility Analysis

Achievable Configuration

Degraded Performance

Burst Handling

Critical Failure Scenario

10x burst (5,000 RPS) for 30 seconds generates 150,000 unsealed events requiring ~60MB TEE-secured memory, exceeding typical enclave limits (256MB-1GB total). Emergency sealing with smaller batches creates throughput collapse due to fixed cryptographic overhead.

High-Velocity Anchoring Strategy

L1 Blockchain Exclusion

Ethereum mainnet: 12-15s block time, 15-30m finality → categorically unsuitable for per-event anchoring

L2 Rollup Utilization

Data Availability Layer

Security Trade-Off Analysis

Delayed Settlement Acceptance

Fork Choice Rule

- • Longest chain with L2 finality gadget

- • Manual escalation for conflicting anchors

- • Conservative interpretation as default

Asynchronous Anchoring Necessity

| Layer | Latency | Purpose |

|---|---|---|

| Local TEE Sealing | 500 ms | Immediate audit readiness, operational monitoring |

| Regional Consensus | 2-5 s | Cross-replica consistency |

| Celestia DA | 2-4 s | Rapid data availability |

| Arbitrum L2 | 1-2 min | Economic finality, regulatory proof |

| Ethereum L1 | 12-15 min | Ultimate settlement (rare) |

Security model: Progressive strengthening - immediate tamper-evidence, near-term economic security, eventual cryptographic finality. Local sealing (500ms) is fundamentally decoupled from global settlement (minutes) due to latency incompatibility between real-time operation and decentralized consensus.

Part 5: Adversarial Stress Testing

Slow Lane Flooding Attack

Exploit Mechanism

- • Synthetic commit intent generation at maximum rate

- • Automated prompt variation and neural paraphrasing

- • Cost asymmetry exploitation (50:1 attacker advantage)

- • Legitimate traffic starvation or degraded mode activation

Attacker: ~$0.001 per request (bandwidth)

Defender: ~$0.05-0.20 per validation (TEE compute)

Mitigation Strategy

100ms CPU puzzle per commit intent, linear attacker cost scaling

Tiered: 10 RPS new, 100 RPS established, 1000 RPS premium

Micropayment requirements for high-volume commit intents

Intentional Timeout Exploitation

Attack Vector

- • Resource-intensive validation path triggers

- • Complex policy nesting and constraint satisfaction

- • Large context retrieval and external data queries

- • Degraded mode activation with validation bypass

Defense Mechanisms

Per-stage budgets for inference, database queries, policy evaluation

Progressive thresholds with anomalous expense logging for policy optimization

Per-client resource quotas with automatic throttling on threshold exceedance

Edge Timing Window Exploitation

Attack Mechanism

- • Sub-millisecond race condition exploitation

- • Precise timing synchronization for detection-to-execution gap

- • Network latency manipulation for coordination

- • Pre-validation execution triggering

Mitigation Approach

TEE-secured monotonic counters with microsecond precision

±1ms enforcement across components with violation detection

Automatic stop and forensic capture on timing violation

Log Ordering Manipulation

Attack Vector

- • Clock skew manipulation via NTP exploitation

- • Network delay injection for event reordering

- • Asymmetric routing for partial ordering control

- • Merkle root manipulation during consensus gaps

Defense Strategy

Lamport timestamps with Byzantine fault tolerance

Merkle root exchange every 100ms with automatic divergence detection

Manual arbitration for unresolvable conflicts with detailed logging

Partial System Desynchronization

Network Partition Attacks

- • Split-brain scenarios with divergent validation outcomes

- • Double-spend opportunities through partition exploitation

- • Coordinated partition timing for maximum impact

- • Gradual desynchronization for subtle inconsistency

CRDT-Based Recovery

Eventual consistency without coordination, explicit conflict identification

Defined tie-breaking rules with conservative default to most restrictive interpretation

Regular partition testing with automatic recovery validation

Part 6: Composability and Distributed Interaction

Chained Gateway Interaction Model

System A → System B → System C Pattern

Each gateway applies independent classification and validation, with nested attestation creating cryptographic proof of complete validation chain. Latency amplifies additively: 500ms per gateway in pessimistic mode.

Validation Certificate Chaining

Classification, validation, policy version

Verification of A, additional validation

Verification of A+B, final authorization

Latency Amplification Analysis

| Chain Length | Min Latency | Mitigation |

|---|---|---|

| 2 Gateways | 1,000 ms | Optimistic mode for non-critical paths |

| 3 Gateways | 1,500 ms | Parallel validation where possible |

| 3+ Gateways | — | Reconsider architecture (hierarchy vs. federation) |

Log Ordering Consistency

Global Clock Dependency

Strong global ordering requires sacrificing availability or accepting single point of failure (CAP theorem implication). Unsatisfiable without centralized coordination.

Causal Ordering Alternative

- • Happens-before graph with vector clocks

- • Explicit concurrent event identification

- • Deterministic merge with defined tie-breaking

Override Authority Conflicts

Hierarchical Delegation

Last-Writer-Wins

Cascading Fail-Closed Mitigation

Circuit Breaker Pattern

Domain-Aware Bypass

Part 7: Cost and Resource Envelope

Slow Lane Cost Estimation

Compute

Storage

Anchoring

Total

Monthly Cost Projections

Scaling Model Under Selective Activation

Fast Lane Dominance

Burst Handling Capacity

Hardware Acceleration Triggers

Latency Trigger

→ GPU hash acceleration, dedicated TEE nodes

50% latency reduction expected

Throughput Trigger

→ Horizontal sharding, additional TEE instances

Linear scaling achievable

Cost Trigger

→ Reserved capacity, hardware procurement

30-50% cost reduction expected

Regulatory Liability Break-Even Analysis

| Violation Type | Penalty Range | Annual Exposure | Hardware Justification |

|---|---|---|---|

| SOX Violation | $1M-$10M per incident | $5M (0.5 incident expectation) | $100K annual |

| GDPR Fine | 4% global revenue | $20M ($500M revenue) | $500K annual |

| EU AI Act High-Risk | 6% global revenue | $30M ($500M revenue) | $750K annual |

| PCI-DSS Violation | $5K-$100K/month + brand damage | $1M annual estimate | $100K annual |

| HIPAA Violation | $100-$50K per violation | $2M annual estimate | $200K annual |

Break-even principle: Hardware investment justified when annual cost < 10% of expected liability exposure, recognizing that hardware reduces but does not eliminate risk. The analysis demonstrates clear economic viability for full hardware-based deployment in high-risk domains.

Go / No-Go Recommendation for Pilot Deployment

Conditional Go Conditions

Phase 1-2 Mitigations Implemented

- ✓ Multi-tier detection with adversarial training

- ✓ Hardware-enforced binding with TEE Gateway

- ✓ Optimistic/Pessimistic/Degraded mode state machine

- ✓ Precise timing thresholds (50ms/500ms/5s enforced)

Restricted Domain Scope

- ✓ Conversational AI with reversible state

- ✓ Financial retail (<$1K, reversible transactions)

- ✗ Excluded: Medical, institutional financial, autonomous

Operational Requirements

- ✓ Real-time monitoring on all failure modes

- ✓ 24/7 human escalation path (15min response)

- ✓ Automatic rollback triggers on criterion violation

- ✓ Integration with existing fraud detection systems

No-Go Conditions (Production)

High-Risk Domains

- ✗ Medical without full TEE implementation

- ✗ High-value financial without redundant validation

- ✗ Autonomous actuation without hardware interlocks

Technical Requirements

- ✗ Multi-gateway chaining without causal ordering

- ✗ Production deployment without adversarial stress testing

- ✗ Missing regulatory compliance verification

- ✗ Incomplete safety certification for critical domains

Testing Gaps

- ✗ No controlled flooding exercises completed

- ✗ Missing timing window fuzzing validation

- ✗ Incomplete chaos engineering for partition recovery

- ✗ Insufficient adversarial validation coverage

Pilot Scope Specification

Traffic Volume

Success Criteria

Final Verdict: Conditional Go with Restricted Scope

Structural Viability Assessment

- ✓ Confirmed - Core design sound with appropriate hardening

- ✓ Achievable - Safety invariants with operational discipline

- ✓ Conditional - Domain-specific compliance requirements

- ✓ Confirmed - Economic sustainability within operational budgets

Production Timeline

Recommendation: The Commit-Bound Dual-Latency Architecture demonstrates structural viability with systematic hardening investment. While multiple critical vulnerabilities require resolution before production deployment, the core design principles are sound. The architecture enables risk-proportional resource allocation, TEE-based validation integrity, and cryptographically verifiable audit trails that satisfy regulatory requirements with manageable overhead. The pilot deployment approval provides empirical validation opportunity while maintaining safety boundaries through restricted domain scope and comprehensive monitoring infrastructure.